North Bridge, GIO e Controller Memoria

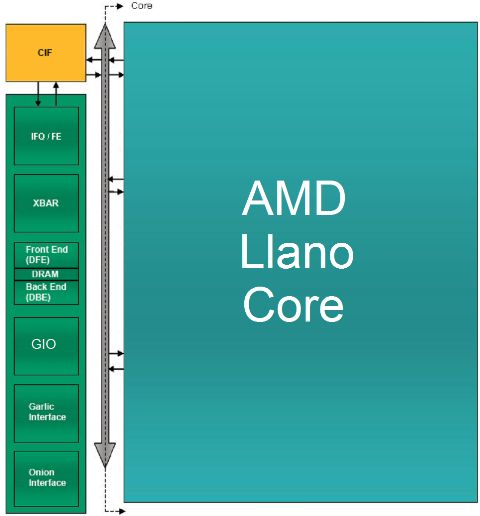

In figura è visibile uno schema a blocchi semplificato del cuore dell’architettura di Llano, ossia i componenti che smistano i dati e gestiscono le comunicazioni con l’esterno: il North Bridge, l’unità GIO e il controller della memoria.

Il blocco di colore verde, contenente gli elementi chiamati IFQ/FE, XBAR, Front End (DFE), DRAM, Back End (DBE), GIO, Garlic Interface e Onion Interface, costituiscono il north bridge on chip, abbreviato in CNB.

Il blocco giallo, chiamato CIF è un blocco di sincronizzazione tra il CNB e ogni core, che convoglia e unifica il flusso di dati da e verso i core con il CNB. Il suo compito è di implementare l’interfaccia CCI, Common Core Interface, Interfaccia comune per i core, che è il punto di accesso unico al CNB per tutti i core.

Questo blocco è quello che implementa l’algoritmo che decide quale dei core può parlare in un dato momento e smista le richieste provenienti da altre parti del chip ai core, come ad esempio il probing delle cache, che è effettuato per vedere se nelle cache dei core è presente un dato più aggiornato rispetto alla memoria RAM.

Veniamo ora ai blocchi costituenti il CNB.

Il blocco IFQ/FE contiene la coda delle richieste delle CPU e della GPU nella IFQ che è dunque una coda unificata.

Comprende anche un blocco di logica, chiamato Front End (FE) che si occupa di gestire le richieste di trasferimento dati da e per i core (che passano per l’interfaccia CCI), di gestire le richieste di trasferimento dati tra l’interfaccia Onion e le CPU, di gestire le richieste di probing della cache delle CPU da parte dei vari componenti e di mantenere la coerenza e la consistenza tra le varie unità.

Il blocco XBAR è il cosiddetto crossbar switch, ossia l’unità che consente il collegamento tra le varie unità collegate al CNB.

E’ in pratica un commutatore digitale che ad ogni istante collega mittente e destinatario di una comunicazione, tra i vari attori presenti nel sistema, come l’interfaccia CCI, il controller RAM, le interfacce Onion e Garlic, eccetera.

I blocchi DRAM, DBE e DFE fanno parte del memory controller (MC).

Il blocco DFE, detto Data Front End, si occupa di selezionare le richieste da mandare alla restante parte del controller RAM e decide tra richieste Onion (coerenti), Garlic (non coerenti) e CCI (coerenti).

Le richieste sono materialmente eseguite dal blocco DBE, detto Data Back End, che sincronizza il CNB con l’interfaccia fisica alle memorie DRAM e gli manda i comandi di trasferimento.

L’interfaccia Garlic (che tradotto letteralmente significa “Aglio”) è un collegamento bidirezionale e a bassa latenza, quindi diretto, tra la GPU e il Data Back End del controller RAM.

Quando il Data Front End ha dato il consenso, la GPU può comunicare con il controller RAM in modo diretto.

L’interfaccia Onion (che tradotto letteralmente significa “Cipolla”) è un collegamento bidirezionale tra la GPU è la coda IFQ. E’ usata per collegare la GPU alle CPU.

Il blocco indicato con GIO (Graphics and I/O) è il blocco che gestisce l’I/O del chip, ed è collegato alla unità XBAR del North Bridge (CNB) per comunicare con i core e il controller RAM e ha un collegamento diretto e privilegiato con la GPU. Questo perché gestisce il controller PCI Express fino a 32 linee, configurabile in vari modi.

Quattro linee sono riservate all’interfaccia UMI (Unified Media Interface), che non è altro che una interfaccia PCI Express a 4 linee dedicata al collegamento con il Fusion Controller Hub (FCH, il south bridge).

Quattro sono riservate per periferiche PCI Express varie, come le schede audio aggiuntive, per non dover gravare sull’FCH e sono configurabili come linee singole, linee doppie, due singole e una doppia o una sola interfaccia x4.

Sedici linee sono utilizzabili per schede video discrete, configurabile in una interfaccia x16 o due interfacce x8, per il CrossFire.

In alternativa le interfacce x8 possono essere configurate come uscite video, per poter usare la tecnologia EyeFinity, perdendo la possibilità del CrossFire/DualGraphics.

Le rimanenti 8 linee sono utilizzate per implementare le interfacce video HDMI, DVI e Display Port.

Il BUS grigio che si vede a fianco del CNB e del CIF è il BUS di collegamento unico su cui si affacciano tutti i core e su cui sono abilitati a comunicare, a turno, dal blocco CIF.

Controller RAM integrato

Il controller RAM di Llano supporta due canali indipendenti a 64 bit di RAM DDR3 con chip da 8 e 16 bit, supporta l’interleaving sui chip e sui canali, utile per incrementare le prestazioni, leggendo dati consecutivi da chip diversi in parallelo, include algoritmi di scheduling per l’apertura e chiusura delle pagine di memoria, ottimizzato in particolare per flussi di scrittura e lettura intervallati, include algoritmi di scheduling per ottimizzare i flussi intervallati di dati dalle interfacce CPU+Onion e Garlic e include un prefetcher hardware.

In particolare le pagine usate dagli accessi GPU sono chiuse immediatamente, perché in genere gli accessi sono streaming, per liberare le pagine per gli accessi CPU, tipicamente più variegati.

I dati caricati dal prefetcher sono mantenuti nel controller stesso e non sono mandati speculativamente nelle cache L1 e L2.

Il prefetcher è in grado di catturare sia andamenti crescenti o decrescenti di accesso anche con spaziatura non unitaria, utilizzando come unità di misura la linea di cache (64 byte) ed è in grado di rilevare anche sequenze separate di accessi. Inoltre Llano può tenere traccia di 8 sequenze di accessi contemporaneamente (l’architettura Stars ne può tenere traccia di 5).

Il controller della memoria di Llano è stato migliorato di molto rispetto ai core Stars. E’ stata migliorata l’efficienza interna e gli algoritmi di prefetching, in particolare il core Llano è in grado di riconoscere meglio i pattern di accesso alla memoria, perché è in grado di associarvi l’effettiva istruzione che accede alla memoria (IP-based prefetching) e quindi non è più distratto da altre istruzioni intermedie. Inoltre sono stati aumentati i buffer interni.

E’ stata incrementata la frequenza RAM supportata fino a 1866 MHz (solo con una DIMM per canale), rispetto ai 1333 MHz della precedente generazione. In compenso è stato tolto il supporto alle memorie DDR2, ai chip a 4 bit e alla correzione ECC, quest’ultima utilizzata tipicamente in ambito server.